Shift Register

FND(Flexible Numeric Display)를 다룬다고 가정해 보자. 한 자리 숫자만을 출력해도 8개의 핀이 필요하다.

이런 경우 시프트 레지스터를 활용하여 하나의 핀으로 8개의 output을 제어할 수 있다. (약간의 delay는 생긴다.)

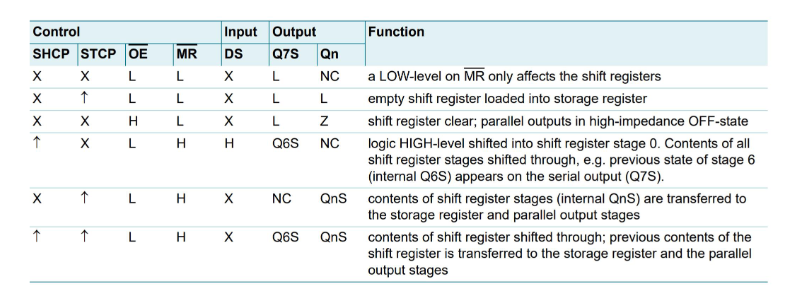

74HC595

Q0 ~ Q7 : parallel output pins of register

DS : Serial data input pin

SHCP : shift register clock pin

STCP : storage register(Latch) clock pin

OE : output enable, Latch의 출력을 끌 수 있다.

MR : master re-clear, 시프트 레지스터를 reset 할 수 있다.

Shift register의 값이 바로 Q0 ~ Q7로 출력되지 않는다.

Latch가 존재하고 Latch clock이 상승할 때, shift register에 저장된 값이 Q0 ~ Q7으로 출력된다.

제어 코드의 흐름은 다음과 같다.

1. DS에 값 입력

2. SHCP에 상승엣지 발생 = 시프트 레지스터에 값 이동

3. 의도하는 타이밍에 따라 STCP에 상승엣지 발생

'electronic' 카테고리의 다른 글

| 라플라스 변환, 전달 함수, 특성 방정식, DC gain (0) | 2024.03.01 |

|---|